SiliconPV 2023, 13th International Conference on Crystalline Silicon Photovoltaics

Silicon Material and Defect Engineering

ttps://doi.org/10.52825/siliconpv.v1i.882

© Authors. This work is licensed under a Creative Commons Attribution 4.0 International License

Published: 27 Feb. 2024

# Influence of Different Post Porosification Cleaning Steps on the Parameters of Porous Silicon Layer Stack

Sarah Sanz<sup>1[https://orcid.org/0009-0002-6530-0963]</sup>, Yves Patrick Botchak Mouafi<sup>1[https://orcid.org/0000-0001-8993-1490]</sup>, Gabriel Micard<sup>1[https://orcid.org/0000-0002-5933-3008]</sup>, Giso Hahn<sup>1[https://orcid.org/0000-0001-8292-1281]</sup>,

and Barbara Terheiden<sup>1</sup>

<sup>1</sup> University of Konstanz, Germany

**Abstract.** To grow a defect-free epitaxial silicon wafer (EpiWafer) on a reorganized porous silicon layer stack, the surface must be closed, smooth and particle-free. A post-porosification cleaning step prior to reorganization should significantly reduce the density of (metallic) particles on the surface. In this paper we systematically investigate the influence of different post-porosification cleaning steps on the porous layer stack. The different cleaning steps have no significant effect on the layer thicknesses. On the other hand, the porosities change after the different cleaning steps. The change in porosity correlates very well with the oxidizing effect of the solution used: SC-1 cleaning has the strongest oxidizing effect, followed by ozone cleaning, piranha cleaning and HCl cleaning. A single HF dip has the smallest effect on porosity, showing the small influence of the native silicon oxide layer formed by aging on porosity. Except for the SC-1 cleaning, the other cleanings show no significant change in the Raman peak shift and therefore in stress compared to the as-etched sample. For the SC-1 cleaning, the increase in Raman peak shift and thus stress correlates well with the increase in porosity. After a reorganization step at 1120°C, it is observed that a higher porosity of the low porosity layer in the stack leads to larger pores.

Keywords: Porous Silicon, Crystalline Silicon, Epitaxial Silicon Wafer, Silicon Surface Cleaning

#### 1. Introduction and Experimental

To grow a defect-free epitaxial silicon wafer (EpiWafer) on top of a reorganized porous silicon layer stack as introduced by Brendel [1], the surface has to be closed, smooth, and particle-free. The presence of (metallic) particles on the surface of the porous layer can negatively affect the reorganization and lead to an increase in the density of structural defects in the EpiWafer. A post-porosification cleaning step prior to the reorganization should significantly reduce the density of (metallic) particles on the surface. In this contribution, we systematically investigate the influence of different post-porosification cleaning steps on the parameters of the porous layer stack and subsequently on the reorganization step.

The porous silicon layer stacks were prepared by anodic electrochemical etching of 156.7×156.7 mm<sup>2</sup> full square, (100)-oriented highly boron-doped (p-type) Cz-Si with a resistivity between 11 and 12 m $\Omega$ cm in an HF:H<sub>2</sub>O:2-Propanol solution in proportions 1:1:1. To obtain a double layer stack with a low-porosity layer (LPL) on top of a high-porosity layer (HPL), the current density was increased from 8.1 mA/cm<sup>2</sup> to 142.4 mA/cm<sup>2</sup> after the formation of the top layer (LPL). All samples were etched with the same parameters. After etching, the reflectance

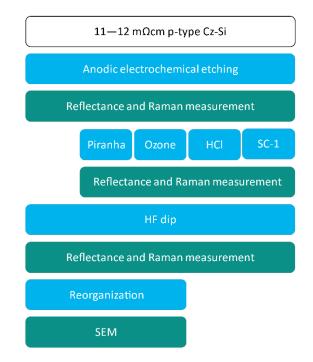

in the visible and up to the infrared spectral range was measured on 30×30 points on each sample to obtain the thicknesses and porosities of the LPL and HPL [2]. In addition, micro-Raman spectroscopy measurements were carried out in order to determine the Raman peak shift of the porous silicon layer stack compared to the silicon bulk which is linked to the residual stress in the porous silicon layer stack. Afterwards, the samples were cleaned in different solutions: Piranha etch (H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub>), ozone cleaning, the so-called SC-1 (NH<sub>3</sub>, H<sub>2</sub>O<sub>2</sub>, and H<sub>2</sub>O) cleaning [3] and HCI (HCI and H<sub>2</sub>O). A second measurement of the reflectance spectra and micro-Raman spectroscopy measurement was then performed. After an HF dip of all previously cleaned samples and samples of a fifth additional group without any cleaning, a third measurement sequence was carried out. The fifth group of samples without cleaning was chosen to illustrate the influence of the native oxide and the aging on the parameters (thickness and porosity) of the porous silicon layer stack. In addition, sister samples cleaned in Piranha and ozone and those of the fifth group without cleaning were reorganized in H<sub>2</sub> under atmospheric pressure for 30 min at 1120°C after a HF dip. To investigate the effect of these cleaning steps on reorganization, scanning electron microscope (SEM) images were taken in top view to check whether the surface is fully closed and free of voids, and in cross-section to examine the shape and size of the pores in the LPL. The process flow is schematically shown in Fig. 1.

Figure 1. Schematical process flow.

## 2. Results

### 2.1 Impact on layer thickness and porosity

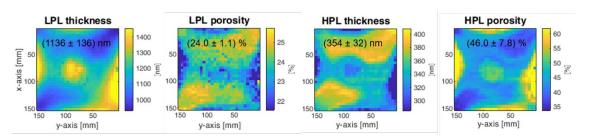

Fig. 2 shows spatially resolved maps of layer thicknesses and porosities of an as-etched porous double layer stack obtained from the fit of reflectance spectra over the whole wafer, as described in [2]. For all samples, the mean value of the LPL thickness is about 1.1  $\mu$ m. Depending on the substrate resistivity, the LPL porosity mean value is about either 22% or 24% as shown in Fig. 3(a). For the HPL, mean values for thickness of about 350 nm and porosity of about 45% were obtained.

Sanz et al. | SiliconPV Conf Proc 1 (2023) "SiliconPV 2023, 13th International Conference on Crystalline Silicon Photovoltaics"

**Figure 2.** Spatially resolved maps of porosity and layer thickness of LPL and HPL of an asetched porous double layer stack. The uncertainty values indicate the spatial variation over the whole wafer (30×30 points) and are a measure of its homogeneity.

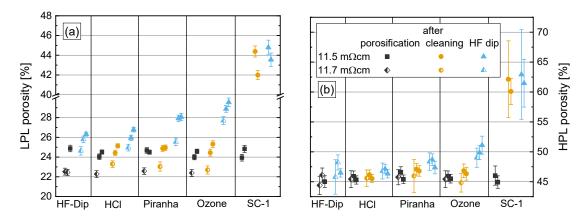

In Fig. 3 mean values of the porosity of LPL (left) and HPL (right) after different cleaning steps are shown. Each group consists of three samples. The difference of about  $2\%_{abs.}$  in the LPL porosity after etching is due to the different resistivity of the substrates used (compare semiclosed and fully closed black squares): the porosity increases with decreasing substrate resistivity (with increasing substrate doping concentration) [4]. For the HCl, Piranha, and ozone cleaning, there is no substantial change in the porosity of LPL and HPL directly after cleaning. This means that the oxidation that occurs during these cleaning steps does not change significantly the porosity. The subsequent HF dip removes the oxide layer on the surface and a significant increase in LPL and HPL porosity is observed. Since the highest porosity increase after the HF dip is observed for ozone cleaning (~  $4\%_{abs.}$  in LPL porosity) followed by Piranha cleaning (~ $3\%_{abs.}$  in LPL porosity), it can be concluded that ozone cleaning has the strongest oxidizing effect.

**Figure 3.** Mean values of the LPL porosity (left) and HPL porosity (right) after different processing steps. The error bars indicate the mean value of the fitting error over the entire sample.

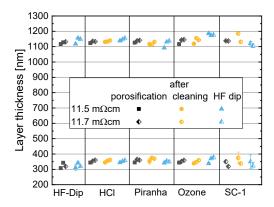

For the samples without a cleaning step after the electrochemical etching, the increase in the LPL porosity after the HF dip due to the removal of the native silicon oxide layer is about  $2\%_{abs.}$  which is of the same order of magnitude as for the samples with HCl cleaning. During SC-1 cleaning, the thin native silicon oxide layer is dissolved from the surface and this is simultaneously re-oxidized due to the strong oxidizing nature of H<sub>2</sub>O<sub>2</sub> [5]. This leads to a fast silicon removal and thus to a drastic increase in LPL and HPL porosity. For this cleaning, the subsequent HF dip has only a minor influence on the porosity. This significant increase in porosity makes SC-1 unsuitable for porous silicon cleaning, since the layers are strongly modified. However, the SC-1 cleaning might be used to fine-tuning the porosity. The different cleaning steps and the subsequent HF dip have no significant influence on the thickness of LPL and HPL, as can be seen in Fig. 4.

**Figure 4.** Mean values of the LPL (top symbols) and HPL (bottom symbols) thickness after different processing steps. The error bars indicate the mean value of the fitting error over the entire sample.

#### 2.2 Effect on residual stress

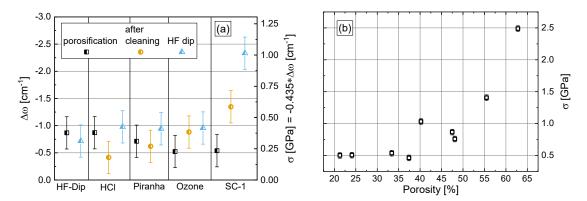

Fig. 5(a) shows the Raman peak shift of the porous silicon double layer stack (front side) to the silicon bulk (backside) and the corresponding residual stress measured after the different processing steps. The stress value was determined according to [6] for backscattering from a (001) surface, where only the third Raman mode is observed and therefore the stress is proportional to the Raman peak shift. Prior to the epitaxial silicon growth after reorganization, the surface of the template should be free of stress to avoid its propagation into the growing Epi-Wafer.

**Figure 5**. In (a) the Raman peak shift  $\Delta \omega$  of the porous silicon double layer stack to the silicon bulk and the corresponding stress after different processing steps is shown. In (b) the residual stress  $\sigma$  of a porous silicon single layer as a function of porosity is shown.

For all samples, tensile stress occurs after anodic electrochemical etching due to the expansion of the porous silicon lattice. This stress induces a red shift of the Raman peak with respect to the silicon bulk [7]. For HCl cleaning, Piranha etch, ozone cleaning, and even after the subsequent HF-dip, there is no remarkable change in the position of the Raman peak: all peak shifts are within the measurement uncertainty. However, an increase of the red shift up to -1.3 cm<sup>-1</sup> is observed after the SC-1 cleaning and up to -2.3 cm<sup>-1</sup> after cleaning and HF dip, respectively, leading to a stress value of up to 1 GPa. This correlates well with the increase in porosity, as shown in the section above, and can be explained by the dependence of the residual stress on porosity, as observed in a previous experiment (see Fig. 5(b)) [8]. The stress in the porous layer remains constant up to about 40% porosity and then starts to increase with increasing porosity.

#### 2.3 Effect on reorganization

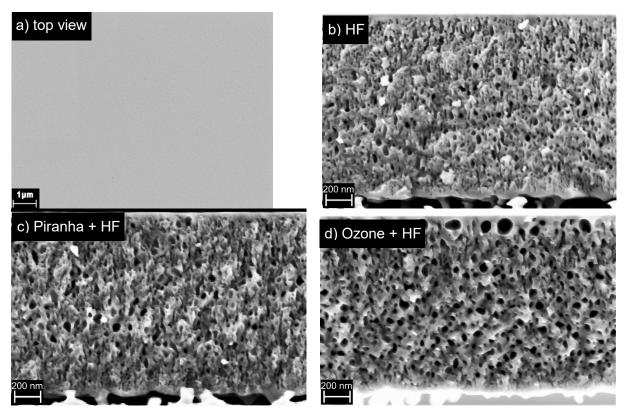

To study the surface closure after the reorganization step, the samples' top view is observed in SEM. Fig. 6(a) shows as an example the top view of the sample with only an HF dip, the top views of the samples from the other two cleanings are similar. It can be clearly seen that the surface is completely closed and free of voids or holes.

In order to compare the influence of the different cleaning steps on reorganization, the cross sections are observed and the shape and size of the pores are compared. SC-1 cleaning has not been considered because the porous layer would detach from the seed wafer during reorganization due to the high porosity after cleaning. Furthermore, HCl cleaning was not taken into account because its impact on the porosity is comparable to that of the single HF dip. Fig. 6 (b)-(d) shows the different SEM cross sections at the same magnification for HF dip, ozone, and Piranha cleaning, each followed by an HF dip.

**Figure 6.** SEM images in (a) top view of a reorganized porous silicon layer stack that has only seen an HF dip prior to reorganization. Cross-sectional views of reorganized porous silicon layer stacks with different cleaning and processing steps (single HF dip (b), Piranha followed by an HF dip (c), and ozone followed by an HF dip (d)) prior to reorganization.

In the cross-sectional analysis, all samples show a closed and void-free surface. Round pores are observed, with pore sizes increasing going from single HF dip to Piranha cleaning and finally to ozone cleaning. This suggests that increased LPL porosity, as previously observed, leads to larger pores, which in turn results in increased pore size in the reorganized state. For the ozone cleaning, there are some larger pores near to the top surface. These pores could increase the surface roughness, which could lead to an increase in the density of structural defects in the resulting EpiWafer.

## 3. Conclusion

In summary, the results demonstrate a strong correlation between changes in porosity and the oxidizing effect of the cleaning solution used after porosification: the more oxidizing the cleaning solution is, the higher is the increase in LPL porosity after an HF dip. The thickness of the porous silicon stack is not influenced by the different cleaning steps. After a reorganization step at 1120°C, it is observed that higher LPL porosity leads to larger pores. With the exception of SC-1 cleaning, the other cleaning steps do not show significant changes in Raman peak shift within measurement uncertainty and therefore in stress compared to the as-etched sample. The increase in Raman peak shift and stress observed for SC-1 cleaning correlates well with the increase in porosity. Except for SC-1 cleaning, which can be used rather to fine-tune the porosity, all other investigated cleaning solutions are suitable for porous silicon cleaning.

### Data availability statement

The data that support the findings of this study and details on the measurement setup are available from the corresponding author upon reasonable request.

### Author contributions

Sarah Sanz: Investigation, Conceptualization, Formal analysis, Writing - Original Draft Yves Patrick Botchak Mouafi: Investigation, Formal analysis, Conceptualization, Writing - Original Draft Gabriel Micard: Software, Writing - Original Draft Giso Hahn: Review & Editing Barbara Terheiden: Conceptualization, Supervision, Funding acquisition, Project administration, Resources

### **Competing interests**

The authors declare no competing interests.

## Funding

Part of this work was financially supported by the German Federal Ministry for Economic Affairs and Climate Action (FKZ 03EE1082B, 03EE1117B). The content is the responsibility of the authors.

### Acknowledgement

The authors would like to thank Nadine Pfändler for the reorganization, Barbara Rettenmaier for technical support and Michael Laumann for SEM usage.

### References

- R. Brendel, "A novel process for ultrathin monocrystalline silicon solar cells on glass," in Proc. 14<sup>th</sup> EU PVSEC, 1997, pp. 1354-1358.

- 2. G. Micard, Y.-P. Botchak Mouafi, B. Terheiden, "Non-destructive spatially resolved characterization of porous silicon layer stacks," in Proc. 12<sup>th</sup> SiliconPV, in press.

- 3. W. Kern, D. Puotinen, "Cleaning solutions based on hydrogen peroxide for use in silicon semiconductor technology," RCA Review. vol.31, no.2, pp.187-206, June, 1970

- 4. Y. P. Botchak Mouafi, N. Birkle, M. Driessen, G. Micard, J. Muerter, R. Sorgenfrei, B. Terheiden, C. Weiss, "Increasing robustness of EpiWafer transfer process leading

to carrier lifetimes of 1.6 ms using large scale production feasible substrate wafers," in Proc. 12<sup>th</sup> SiliconPV, in press.

- 5. K. A. Reinhardt, W. Kern, "Handbook of silicon wafer cleaning technology," William Andrew Inc., 2008.

- I. De Wolf, "Micro-Raman spectroscopy to study local mechanical stress in silicon integrated circuits," Semiconductor Science and Technology, vol.11, no.2, pp. 139–154, Nov., 1996, doi: https://doi.org/10.1088/0268-1242/11/2/001

- K. Barla, G. Bomchil, R. Herino, J. C. Pfister, J. Baruchel, "X-ray topographic characterization of porous silicon layers," Journal of Crystal Growth, vol.68, no.3, pp. 727– 732, Oct., 1984, doi: https://doi.org/10.1016/0022-0248(84)90110-6

- S. Manotas, F. Agulló-Rueda, J. D. Moreno, F. Ben-Hander, R. Guerrero-Lemus, J. M. Martínez-Duart, "Determination of stress in porous silicon by micro-Raman spectroscopy," Physica Status Solidi A., vol.182, no.1, pp. 245–248, Nov., 2000, doi: https://doi.org/10.1002/1521-396X(200011)182:1<245::AID-PSSA245>3.0.CO;2-W.